Fabrikazio Elektronikoko Zerbitzu Integralak, zure produktu elektronikoak PCB eta PCBAtik erraz lortzen lagunduko dizute

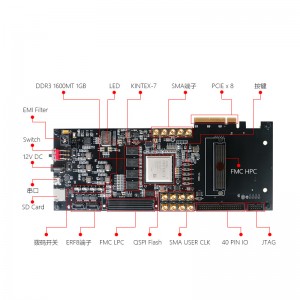

FPGA Xilinx K7 Kintex7 PCIe zuntz optikozko komunikazioa

- DDR3 SDRAM: 16 GB DDR3 64 biteko busa, 1600 Mbps-ko datu-tasa

- QSPI Flash: 128mbit-eko QSPIFLASH zati bat, FPGA konfigurazio fitxategietarako eta erabiltzaileen datuak gordetzeko erabil daitekeena.

- PCLEX8 interfazea: PCLEX8 interfazea ordenagailuaren plaka basearen PCIE komunikazioarekin komunikatzeko erabiltzen da. PCI Express 2.0 estandarra onartzen du. Kanal bakarreko komunikazio-tasa 5 Gbps-koa izan daiteke.

- USB UART serieko ataka: Serieko ataka bat, miniUSB kablearen bidez ordenagailura konektatzen dena serieko komunikazioa egiteko.

- Mikro SD txartela: Microsd txartelaren eserleku osoa, Microsd txartel estandarra konekta dezakezu

- Tenperatura sentsorea: LM75 tenperatura sentsore txipa, garapen plakaren inguruko ingurumen-tenperatura kontrolatu dezakeena

- FMC luzapen-ataka: FMC HPC bat eta FMCLPC bat, hainbat hedapen-txartel estandarrekin bateragarriak izan daitezkeenak

- ERF8 abiadura handiko konexio terminala: 2 ERF8 ataka, ultra-abiadura handiko seinaleen transmisioa onartzen dutenak 40 pineko luzapena: 2,54 mm-ko 40 pineko IO interfaze orokor bat gordeta, O eraginkorrak 17 bikote ditu, 3,3 V onartzen ditu

- Mailaren eta 5V-ko mailaren konexio periferikoak 1O interfaze orokor desberdinetako periferiko periferikoak konekta ditzake.

- SMA terminala; 13 kalitate handiko urrez estalitako SMA buru, erabiltzaileek abiadura handiko AD/DA FMC hedapen txartelekin elkarlanean aritzeko komenigarria dena seinaleak biltzeko eta prozesatzeko.

- Erlojuaren kudeaketa: Erloju anitzeko iturria. Hauek barne hartzen dute 200 MHz-ko sistemaren erloju diferentzialaren iturria, SIT9102.

- Kristal diferentzial oszilatzailea: 50MHz-ko kristala eta SI5338P erloju programagarriaren kudeaketa txipa: honekin ere hornituta dago

- 66MHz EMCCLK. Zehaztasunez egokitu daiteke erabilera desberdinetako erloju-maiztasunetara.

- JTAG ataka: 10 puntada 2,54 mm-ko JTAG ataka estandarra, FPGA programak deskargatu eta arazteko

- Sub-berrezartze tentsioaren monitorizazio txipa: ADM706R tentsioaren monitorizazio txiparen zati bat, eta botoia duen botoiak berrezartze seinale globala ematen dio sistemari

- LED: 11 LED argi, plaka-txartelaren energia-iturria adierazten dute, config_done seinalea, FMC

- Energia adierazle seinalea eta 4 erabiltzaile LED

- Giltza eta etengailua: 6 giltza eta 4 etengailu FPGA berrezartzeko botoiak dira,

- B programaren botoia eta 4 erabiltzaile-tekla osatuta daude. 4 labana bakarreko etengailu bikoitza

Idatzi zure mezua hemen eta bidali iezaguzu

Produktuen kategoriak

-

Telefonoa

-

Posta elektronikoa

-

Whatsapp

-

Skype

-

Skype

-

Skype